Oblia (electrònica)

En microelectrònica, una oblia és una fina planxa de material semiconductor, com per exemple cristall de silici, sobre la qual es construeixen microcircuits mitjançant tècniques de dopat (per exemple, difusió o implantació d'ions), gravat químic i deposició de diversos materials. Les oblies tenen, d'aquesta manera, una importància clau en la fabricació de dispositius semiconductors tals com els circuits integrats o les cèl·lules solars.[1]

Es fabriquen en diverses grandàries que van des d'1 polzada (25,4 mm) a 11,8 polzades (300 mm) i calibres de l'ordre de mig mil·límetre. Generalment s'obtenen mitjançant el tall de grans cilindres de material semiconductor utilitzant discos de diamant per després ser polides per una de les seves cares.

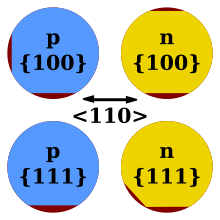

En les oblies per sota de 200 mm normalment s'indiquen els plànols cristal·logràfics d'alta simetria mentre que en les antigues (aquelles amb diàmetre inferior a 100 mm) s'indiquen l'orientació de l'oblia i el tipus de dopat (veure il·lustració). Les oblies modernes compten amb una osca per referir aquesta informació, evitant així el desaprofitament de material [1].

L'orientació és important mentre moltes de les propietats electròniques i estructurals dels cristalls simples són altament anisotròpiques. Per exemple, la formació de plànols definits en els cristalls en les oblies solament succeeix en algunes adreces concretes. Gravant les oblies en aquestes adreces facilita la seva posterior divisió en xips individuals de manera que els milers de milions d'elements d'una oblia mitjana poden ser separats en multitud de circuits individuals.

Integració

[modifica]A partir de les oblies s'inicia l'estampat en superfície dels circuits integrats mitjançant fotolitografia, nanolitografia i altres tècniques.

Prova de les oblies

[modifica]El testeig de les oblies té lloc durant la fabricació dels dispositius semiconductors. En aquest pas, realitzat abans de la divisió de l'oblia, es proven tots els circuits integrats individuals presents en ella per comprovar que no hi hagi errors funcionals. Aquestes proves són dutes a terme per un dispositiu especial anomenat emprovador d'oblies o wafer prober, sent les més comunes: Wafer Sort (W), Wafer Final Test (WFT), Electronic Die Sort (EDS) i Circuit Probe (CP).

Quan un xip concret supera tots aquests patrons de prova, s'emmagatzema la seva posició en l'oblia per al seu ús posterior durant la fase d'encapsulació. De vegades un xip compta amb recursos interns de recanvi disponibles per a una eventual reparació (per exemple, els CI dedicats a memòria flaix). Si un xip no supera les proves, poden utilitzar-se aquestes parts; no obstant això, si no és possible aplicar la redundància de components o aquesta no soluciona el problema, el xip és considerat defectuós i es descarta. Els circuits no vàlids solen marcar-se amb una petita gota de tinta al centre, així com en un arxiu que funciona com a mapa de l'oblia anomenat wafermap on es classifiquen els xips com a vàlids o no. Aquest arxiu és enviat llavors a la zona d'assemblat de xips, on solament prenen aquells circuits marcats com a adequats.

En alguns casos molt específics, un xip que passa solament algunes de les proves pot ser utilitzat igualment, però amb certes limitacions. L'exemple més comú d'això és un microprocessador en el qual solament una part de l'elegància integrada funciona. En aquest cas, el processador pot ser que sigui venut com a component de baix cost en comptar amb menys memòria i per tant, proporcionar un menor rendiment. D'altra banda, una vegada que els xips defectuosos han estat identificats, aquests poden ser emprats pel personal de la cadena de producció per a proves del sistema d'assemblat.

Els continguts de tots els patrons de prova i la seqüència en què són aplicats a un circuit integrat formen part del que es coneix com a programa de prova.

Una vegada empaquetats, els xips seran comprovats de nou durant la fase de prova del circuit integrat, normalment amb patrons iguals o molt similars als anteriors. Per aquest motiu, pot pensar-se que la comprovació de les oblies resulta innecessària i redundant. En realitat no és així, ja que la retirada dels xips defectuosos suposa un important estalvi al no empaquetar en la següent fase dispositius defectuosos. No obstant això, en cas que les proves de les oblies resultin més cares que l'empaquetat dels dispositius defectuosos pot saltar-se el primer pas, passant tots els xips a la fase d'assemblat.

Estàndards de grandària

[modifica]Adaptació de [2] Arxivat 2008-02-20 a Wayback Machine.

- 1 polzada.

- 2 polzades (50,8 mm). Calibre 275 µm.

- 3 polzades (76,2 mm). Calibre 375 µm.

- 4 polzades (100 mm). Calibre 525 µm.

- 5 polzades (125 mm). Calibre 625 µm.

- 6 polzades (150 mm). Calibre 675 µm.

- 8 polzades (200 mm). Calibre 725 µm.

Vegeu també

[modifica]Referències

[modifica]- ↑ Phillip A. Laplante. Comprehensive dictionary of electrical engineering. 2nd. CRC Press, 2005. ISBN 978-0-8493-3086-5.

Enllaços externs

[modifica]- Detalls sobre els semiconductors - Facultat d'Enginyeria. Universitat de Kiel, Alemanya. (anglès)