Lògica de tres estats

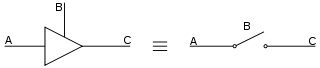

En electrònica digital, un buffer de tres estats o tres estats és un tipus de memòria intermèdia digital que té tres estats estables: un estat de sortida alta, un estat de sortida baixa i un estat d'alta impedància. En l'estat d'alta impedància, la sortida del buffer es desconnecta del bus de sortida, permetent que altres dispositius condueixin el bus sense interferències del buffer de tres estats. Això pot ser útil en situacions en què diversos dispositius estan connectats al mateix bus i necessiten accedir-hi per torns. Els sistemes que implementen la lògica de tres estats al seu bus es coneixen com a bus de tres estats o bus de tres estats.[1]

| ENTRADA | SORTIDA | |

|---|---|---|

| A | B | C |

| 0 | 0 | Z (alta impedància) |

| 1 | Z (alta impedància) | |

| 0 | 1 | 0 |

| 1 | 1 | |

Els buffers de tres estats s'utilitzen habitualment en sistemes basats en bus, on diversos dispositius estan connectats al mateix bus i necessiten compartir-lo. Per exemple, en un sistema informàtic, es poden connectar diversos dispositius com la CPU, la memòria i els perifèrics al mateix bus de dades. Per garantir que només un dispositiu pot transmetre dades al bus a la vegada, cada dispositiu està equipat amb un buffer de tres estats. Quan un dispositiu vol transmetre dades, activa el seu buffer de tres estats, que connecta la seva sortida al bus i li permet transmetre dades. Quan la transmissió s'ha completat, el dispositiu desactiva el seu buffer de tres estats, que desconnecta la seva sortida del bus i permet que un altre dispositiu accedeixi al bus.[2]

Els buffers de tres estats es poden implementar mitjançant portes, flip-flops o altres circuits lògics digitals. Són útils per reduir la diafonia i el soroll en un bus, i per permetre que diversos dispositius comparteixin el mateix bus sense interferències.[3]

Usos[modifica]

El concepte bàsic del tercer estat, alta impedància (Hi-Z), és eliminar efectivament la influència del dispositiu de la resta del circuit. Si més d'un dispositiu està connectat elèctricament a un altre dispositiu, sovint s'utilitza posar una sortida a l'estat Hi-Z per evitar curtcircuits, o un dispositiu condueix a alt (1 lògic) contra un altre dispositiu que passa a baix (0 lògic).

Els buffers de tres estats també es poden utilitzar per implementar multiplexors eficients, especialment aquells amb un gran nombre d'entrades.[4]

Els buffers de tres estats són essencials per al funcionament d'un bus electrònic compartit.

La lògica de tres estats pot reduir el nombre de cables necessaris per conduir un conjunt de LED (multiplexació triestatal o Charlieplexing).

Referències[modifica]

- ↑ «Tri-state Logic» (en anglès). https://embeddedartistry.com.+[Consulta: 15 juliol 2023].

- ↑ eeeguide. «What is Tristate Logic or Three State Logic Circuit?» (en anglès). https://www.eeeguide.com,+28-10-2022.+[Consulta: 15 juliol 2023].

- ↑ «Logic Circuit: 3 State Buffer (1) | Toshiba Electronic Devices & Storage Corporation | Americas – United States» (en anglès). https://toshiba.semicon-storage.com.+[Consulta: 15 juliol 2023].

- ↑ Hill, Winfield. The Art of Electronics (en anglès). Cambridge University Press, 1989, p. 495–497. ISBN 0-521-37095-7.