Controlador d'interrupció programable

En informàtica, un controlador d'interrupció programable (PIC) és un circuit integrat que ajuda a un microprocessador (o CPU) a gestionar les sol·licituds d'interrupció (IRQ) procedents de múltiples fonts diferents (com ara dispositius d'E/S externs) que es poden produir simultàniament.[1] Ajuda a prioritzar les IRQ perquè la CPU canviï l'execució al gestor d'interrupcions (ISR) més adequat després que el PIC avaluï les prioritats relatives de les IRQ. Els modes habituals de prioritat d'interrupció inclouen prioritats dures, prioritats rotatives i prioritats en cascada. Els PIC sovint permeten mapejar l'entrada a les sortides d'una manera configurable. A l'arquitectura de l'ordinador, els PIC s'incorporen normalment a un xip southbridge l'arquitectura interna del qual està definida pels estàndards del venedor del chipset.[2]

Característiques comunes[modifica]

Els PIC solen tenir un conjunt comú de registres: registre de sol·licitud d'interrupció (IRR), registre en servei (ISR) i registre de màscara d'interrupció (IMR). L'IRR especifica quines interrupcions estan pendents de reconeixement, i normalment és un registre simbòlic al qual no es pot accedir directament. El registre ISR especifica quines interrupcions s'han reconegut, però encara estan esperant un final d'interrupció (EOI). L'IMR especifica quines interrupcions s'han d'ignorar i no reconèixer. Un esquema de registre senzill com aquest permet que fins a dues sol·licituds d'interrupció diferents siguin pendents alhora, una esperant el reconeixement i una altra esperant l'EOI.[3]

Hi ha una sèrie d'esquemes de prioritats comuns als PIC, com ara prioritats dures, prioritats específiques i prioritats rotatives.

Les interrupcions poden ser activades per vora o per nivell.

Hi ha diverses maneres habituals de reconèixer que s'ha completat una interrupció quan s'emet una EOI. Aquests inclouen especificar quina interrupció s'ha completat, utilitzar una interrupció implícita que s'ha completat (normalment la prioritat més alta pendent a l'ISR) i tractar el reconeixement de la interrupció com a EOI.[4]

Tipus coneguts[modifica]

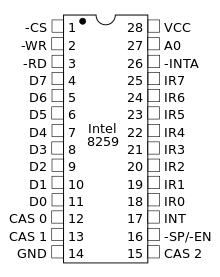

Un dels PIC més coneguts, el 8259A, es va incloure a l'ordinador x86. En els temps moderns, això no s'inclou com a xip separat en un PC x86, sinó com a part del chipset southbridge de la placa base. En altres casos, s'ha substituït pels nous controladors d'interrupció programables avançats que admeten més sortides d'interrupció i esquemes de prioritat més flexibles.

Referències[modifica]

- ↑ Christopher Small; Stephen Manley "A Revisitation of Kernel Synchronization Schemes".

- ↑ «Programmable Interrupt Controller - an overview | ScienceDirect Topics» (en anglès). [Consulta: 3 desembre 2023].

- ↑ «Programmable Interrupt Controllers: A New Architecture - Architectures and Processors blog - Arm Community blogs - Arm Community» (en anglès), 20-07-2015. [Consulta: 3 desembre 2023].

- ↑ Lutsyk, Petro; Oberhauser, Jonas; Paul, Wolfgang J. Advanced Programmable Interrupt Controllers (APICs) (en anglès). Cham: Springer International Publishing, 2020, p. 505–563. DOI 10.1007/978-3-030-43243-0_12. ISBN 978-3-030-43243-0.