Lògica NAND

Tots els sistemes lògics poden ser convertits a circuits amb portes NAND, tal com va demostrar matemàticament Henry M. Sheffer l'any 1913 en la revista Transactions of the American Mathematical Society (Sheffer 1913). Això també aplica per a les portes NOR. En principi, qualsevol funció lògica combinatòria es pot realitzar amb prous portes NAND.

NAND[modifica]

Una porta NAND és una porta AND negada. Té la següent taula de veritat:

| |||||||||||||||||||||

|

Q = A NAND B

| |||||||||||||||||||||

Creació d'altres portes usant portes NAND[modifica]

Una porta NAND és una porta universal, és a dir: qualsevol altra porta pot ser representada per una combinació de portes NAND.

NOT[modifica]

Una porta NOT pot ser creada unint els inputs d'una NAND gate. Com que una porta NAND és equivalent a una porta AND seguida d'una porta NOT, ajuntant els inputs d'una porta NAND s'acaba obtenint una porta NOT.

| Porta NOT desitjada | Construcció amb NAND | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

|

| |||||||||

| Q = NOT(A) | = A NAND A | |||||||||

| ||||||||||

AND[modifica]

Una porta AND pot ser creada invertint l'output d'una porta NAND, com es mostra a continuació:

| Porta AND desitjada | Construcció amb NAND | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||||||

| Q = A AND B | = (A NAND B) NAND (A NAND B) | ||||||||||||||||||||

| |||||||||||||||||||||

OR[modifica]

Si la taula de veritat d'una porta NAND és examinada o si s'apliquen les lleis de De Morgan, es pot veure que si qualsevol dels inputs és 0, llavors l'output serà 1. En una porta OR, tanmateix, l'output haurà de ser 1 si qualsevol dels inputs és 1. És per això que, si els inputs s'inverteixen, qualsevol input alt -1- causarà un output alt.

| Porta OR desitjada | Construcció amb NAND | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||||||

| Q = A OR B | = (A NAND A) NAND (B NAND B) | ||||||||||||||||||||

| |||||||||||||||||||||

NOR[modifica]

Una porta NOR és una porta OR amb l'output invertit. L'output serà alt -1- quan ni l'input A ni el B siguin alts.

| Porta NOR desitjada | Construcció amb NAND | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||||||

| Q = A NOR B | = [ (A NAND A) NAND (B NAND B) ] NAND [ (A NAND A) NAND (B NAND B) ] | ||||||||||||||||||||

| |||||||||||||||||||||

XOR[modifica]

Una porta XOR pot ser creada connectant quatre portes NAND com es mostra a continuació. Aquesta construcció comporta un retard de propagació tres vegades més gran que el d'una simple porta NAND.

| Porta XOR desitjada | Construcció amb NAND | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||||||

| Q = A XOR B | = [ A NAND (A NAND B) ] NAND [ B NAND (A NAND B) ] | ||||||||||||||||||||

| |||||||||||||||||||||

Alternativament, l'imput B de la porta XNOR amb el retard de propagació de 3 portes pot ser invertit. Aquesta construcció usa cinc portes enlloc de quatre:

| Porta desitjada | Construcció amb NAND |

|---|---|

|

|

| Q = A XOR B | = [ B NAND (A NAND A) ] NAND [ A NAND (B NAND B) ] |

XNOR[modifica]

Una porta XNOR pot ser creada connectant l'output de 3 portes NAND (connectades com si fossin una porta OR) i l'output de la porta NAND als inputs respectius de la porta NAND. Aquesta construcció comporta un retard de propagació tres vegades més gran que el d'una simple porta NAND i usa fins a cinc portes.

| Porta XNOR desitjada | Construcció amb NAND | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||||||

| Q = A XNOR B | = [ (A NAND A) NAND (B NAND B) ] NAND (A NAND B) | ||||||||||||||||||||

| |||||||||||||||||||||

Alternativament, es pot usar la versió de 4 portes d'una porta XOR amb un inversor. Aquesta construcció té una propagació de quatre cops (enlloc de tres vegades) el d'una simple porta NAND.

| Porta desitjada | Construcció amb NAND |

|---|---|

|

|

| Q = A XNOR B | = { [ A NAND (A NAND B) ] NAND [ B NAND (A NAND B) ] } NAND { [ A NAND (A NAND B) ] NAND [ B NAND (A NAND B) ] } |

MUX[modifica]

UN multiplexor o porta MUX és una porta de tres inputs que usa una de les entrades, que rep el nom de bit selector, per seleccionar un dels altres dos inputs, anomenats bits de dades, que donarà com a output.[1]

| Porta MUX desitjada | Construcció amb NAND | |||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Q = [ A AND NOT(S) ] OR (B AND S) |

= [ A NAND (S NAND S) ] NAND (B NAND S) | |||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||

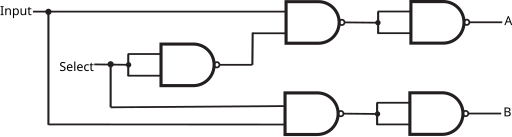

DEMUX[modifica]

Un demultiplexor fa la funció oposada a un multiplexor: agafa un únic input i el retransmet en l'output indicat pel bit selector.[1]

| Porta DEMUX desitjada | Construcció amb NAND | |||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||

Enllaços externs[modifica]

- TTL NAND i portes AND - Tot sobre circuits

- Passos per derivar XOR a partir de portes NAND

- Portes NAND Arxivat 2016-11-21 a Wayback Machine., Demostració d'una simulació iterativa d'un circuit de portes NAND creat amb el simulador Teahlab.

Referències[modifica]

- ↑ 1,0 1,1 Nisan, N. & Schocken, S., 2005. In: From NAND to Tetris: Building a Modern Computer from First Principles. s.l.:The MIT Press, p. 20. Available at: http://www.nand2tetris.org/chapters/chapter%2001.pdf Arxivat 2017-01-10 a Wayback Machine.

Bibliografia[modifica]

- Lancaster, Don. TTL Cookbook. 1st. Indianapolis, IN: Howard W Sams, 1974, p. 126–135. ISBN 0-672-21035-5.

- Sheffer, H. M. «A set of five independent postulates for Boolean algebras, with application to logical constants». Transactions of the American Mathematical Society, 14, 1913, p. 481–488. DOI: 10.2307/1988701.