Extensió de l'adreça física

En informàtica, l'extensió d'adreça física (PAE), de vegades anomenada extensió d'adreça de pàgina,[1] és una característica de gestió de memòria per a l'arquitectura x86. PAE va ser introduït per primera vegada per Intel al Pentium Pro, i més tard per AMD en el processador Athlon.[2] Defineix una jerarquia de taula de pàgines de tres nivells (en lloc de dos), amb entrades de taula de 64 bits cadascua en lloc de 32, permetent que aquestes CPU accedeixin directament a un espai d'adreces físiques més gran que 4 gigabytes (2³² bytes).

L'estructura de la taula de pàgines que utilitzen les CPU x86-64 quan funcionen en mode llarg amplia encara més la jerarquia de la taula de pàgines a quatre o més nivells, ampliant l'espai d'adreces virtuals i utilitza bits d'adreces físiques addicionals a tots els nivells de la taula de pàgines, ampliant el nivell físic. espai d'adreces. També utilitza el bit superior de l'entrada de la taula de pàgines de 64 bits com a bit sense execució o "NX", cosa que indica que el codi no es pot executar des de la pàgina associada. La funció NX també està disponible en mode protegit quan aquestes CPU estan executant un sistema operatiu de 32 bits, sempre que el sistema operatiu habiliti PAE.

Història[modifica]

PAE es va implementar per primera vegada a l'Intel Pentium Pro l'any 1995,[3] encara que els chipsets que l'acompanyaven normalment no tenien suport per als bits d'adreça addicionals necessaris.[4]

PAE és compatible amb els processadors Pentium Pro, Pentium II, Pentium III i Pentium 4. Els primers processadors de la família Pentium M ("Banias") introduïts el 2003 també admeten PAE; tanmateix, no mostren el senyalador de suport PAE a la seva informació CPUID.[5] Això es va solucionar en una revisió posterior del nucli "Dothan" el 2005. També estava disponible en processadors AMD, inclòs l'AMD Athlon [6][7] (encara que els chipsets estan limitats a l'adreçament de 32 bits)[8] i models de processadors AMD posteriors. Quan AMD va definir la seva extensió de 64 bits de l'arquitectura x86 estàndard de la indústria, AMD64 o x86-64, també van millorar el sistema de paginació en " mode llarg " basat en PAE.[9] Admet adreces virtuals de 64 bits [10] (p24) (A Juliol 2023[update], 48 bits estan implementats en alguns processadors i 57 bits estan implementats en altres [10] :{{{1}}}),[11] adreces físiques de 52 bits,[10] (p24)i inclou la funcionalitat de bits NX. Quan s'inicialitza el processador x86-64, cal que s'habiliti la funció PAE abans que el processador passi del mode heretat al mode llarg.[9]

Disseny[modifica]

Amb PAE, l'entrada de la taula de pàgines de l'arquitectura x86 s'amplia de 32 a 64 bits. Això permet més espai per a l'adreça física de la pàgina, o el camp "número de marc de pàgina", a l'entrada de la taula de pàgines. En les implementacions inicials de PAE, el camp del número de trama de pàgina es va ampliar de 20 a 24 bits. La mida del "byte offset" de l'adreça que es tradueix encara és de 12 bits, de manera que la mida total de l'adreça física augmenta de 32 bits fins a 36 bits (és a dir, de 20+12 a 24+12). Això va augmentar la memòria física que teòricament pot adreçar la CPU de 4 GB fins a 64 GB.

Als primers processadors que van donar suport a PAE, el suport per a adreces físiques més grans és evident en el pinout del seu paquet, amb les designacions de pins d'adreça que van fins a A35 en lloc d'aturar-se a A31.[12] Les famílies de processadors posteriors utilitzen interconnexions com Hypertransport o QuickPath Interconnect, que no tenen senyals d'adreces de memòria dedicades, de manera que aquesta relació és menys evident. La mida de 32 bits de l'adreça virtual no es modifica, de manera que el programari d'aplicació habitual continua utilitzant instruccions amb adreces de 32 bits i (en un model de memòria plana) es limita a 4 gigabytes d'espai d'adreces virtuals. Els sistemes operatius que admeten aquest mode utilitzen taules de pàgines per mapejar els 4 GB d'espai d'adreces virtuals a la memòria física, que, depenent del sistema operatiu i de la resta de la plataforma de maquinari, pot ser tan gran com 64 GB. El mapeig s'aplica normalment per separat per a cada procés, de manera que la memòria RAM addicional és útil tot i que cap procés únic pot accedir-hi tot alhora.

El treball posterior associat amb el desenvolupament d'AMD de l'arquitectura x86-64 va ampliar la mida teòrica possible de les adreces físiques a 52 bits.[13] (p24)

Estructures de taules de pàgines[modifica]

Paginació de 32 bits, pàgines de 4 KiB, sense PAE[modifica]

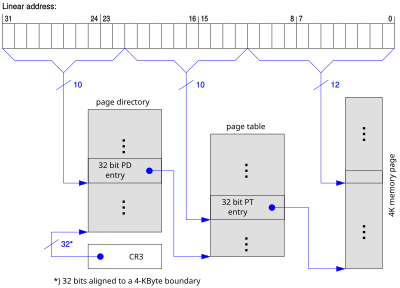

En mode protegit amb la paginació activada (bit 31, PG, del registre de control CR0 està establert), però sense PAE, els processadors x86 utilitzen un esquema de traducció de pàgines de dos nivells. El registre de control CR3 conté l'adreça física alineada a la pàgina d'un sol 4 Directori de pàgines llargues KB. Es divideix en 1024 entrades de directori de pàgines de quatre bytes que al seu torn, si són vàlides, contenen les adreces físiques alineades a les pàgines de les taules de pàgines, cadascuna de 4 KB de mida. De manera similar, consisteixen en 1.024 entrades de taula de pàgines de quatre bytes que, si són vàlides, contenen les adreces físiques alineades a la pàgina de 4 KB de pàgines llargues de memòria física (RAM).

Paginació de 32 bits, pàgines de 4 MiB, sense PAE[modifica]

Les entrades del directori de pàgines tenen un indicador addicional en bits 7, anomenat PS (per a la mida de la pàgina). Si el sistema ha establert aquest bit a 1, l'entrada del directori de pàgines no apunta a una taula de pàgines sinó a un únic i gran 4 Pàgina MB (Extensió de mida de la pàgina).

Paginació de 32 bits, pàgines de 4 KiB, amb PAE[modifica]

Habilitant PAE (mitjançant la configuració del bit 5, PAE, del registre del sistema CR4) provoca grans canvis en aquest esquema. Per defecte, la mida de cada pàgina es manté com a 4 KB. Cada entrada de la taula de pàgines i del directori de pàgines es converteix en 64 bits de llarg (8 bytes), en lloc de 32 bits, per permetre bits d'adreça addicionals. Tanmateix, la mida de cada taula no canvia, de manera que tant la taula com el directori tenen ara només 512 entrades. Com que això només permet la meitat de les entrades de l'esquema original, s'ha afegit un nivell addicional de jerarquia, de manera que el registre del sistema CR3 ara apunta físicament a una taula de punters de directoris de pàgines, una taula curta que conté quatre punters als directoris de pàgines.

Suport 64 les adreces de bits a la taula de pàgines és un canvi significatiu, ja que permet fer dos canvis a l'adreçament del processador. En primer lloc, el caminador de la taula de pàgines, que utilitza adreces físiques per accedir a la taula de pàgines i al directori, ara pot accedir a adreces físiques superiors a les adreces físiques de 32 bits admeses en sistemes sense PAE. Des de CR3, el caminador de la taula de pàgines pot accedir a directoris de pàgines i taules que es troben més enllà de l'interval de 32 bits. En segon lloc, l'adreça física de les dades a les quals s'accedeix (emmagatzemades a la taula de pàgines) es pot representar com una adreça física més gran que les adreces de 32 bits suportades en un sistema sense PAE. De nou, això permet que els accessos a les dades accedeixin a regions de memòria física més enllà del rang de 32 bits.[14]

Paginació de 32 bits, pàgines de 2 MiB, amb PAE[modifica]

Les entrades del directori de pàgines tenen un indicador addicional en bits 7, anomenat PS (per a la mida de la pàgina). Si el sistema ha establert aquest bit a 1, l'entrada del directori de pàgines no apunta a una taula de pàgines sinó a un únic i gran 2 Pàgina MB (Extensió de mida de la pàgina).

Resum de paginació de 32 bits[modifica]

En tots els formats de taula de pàgines compatibles amb IA-32 i x86-64, els 12 bits menys significatius de l'entrada de la taula de pàgines són interpretats per la unitat de gestió de memòria o estan reservats per a l'ús del sistema operatiu. En els processadors que implementen la funció "no executar" o "inhabilitar l'execució", el bit més significatiu (bit 63) és el bit NX. Els següents onze bits més significatius (bits 52 a 62) estan reservats per a l'ús del sistema operatiu tant per les especificacions d'arquitectura d'Intel com d'AMD. Així, dels 64 bits de l'entrada de la taula de pàgines, 12 bits d'ordre baix i 12 d'ordre superior tenen altres usos, deixant 40 bits (del 12 al 51) per al número de pàgina física. Combinat amb 12 bits de "desplaçament dins de la pàgina" de l'adreça lineal, un màxim de 52 bits estan disponibles per adreçar la memòria física. Això permet una configuració màxima de RAM de 252 bytes, o 4 petabytes (uns 4,5×10 15 bytes).

Paginació x86-64[modifica]

Als processadors x86-64 en mode llarg natiu, l'esquema de traducció d'adreces utilitza PAE però afegeix una quarta taula, el nivell de mapa de pàgines de 512 entrades i amplia la taula de punters del directori de pàgines a 512 entrades en lloc de l'original 4 entrades que té en mode protegit. Això vol dir que 48 bits es tradueixen del número de pàgina virtual, donant un espai d'adreces virtuals de fins a 256 TB. Per a alguns processadors, es pot activar un mode amb una cinquena taula, el nivell de mapa de pàgines de 512 entrades de la 5 taula; això vol dir que 57 bits es tradueixen del número de pàgina virtual, donant un espai d'adreces virtuals de fins a 128 PB:[15] 141–153 a les entrades de la taula de pàgines, a l'especificació original, 40 bits s'implementen del número de pàgina física.

Referències[modifica]

- ↑ Dual-Core Intel® Xeon® Processor 2.80 GHz Specification Update (en anglès). Intel Corporation, octubre 2006, p. 18.

- ↑ «Appendix E». A: AMD Athlon™ Processor x86 Code Optimization Guide (en anglès). Revision K. AMD, Inc., febrer 2002, p. 250.

- ↑ T. Shanley. Pentium Pro and Pentium II System Architecture (en anglès). Addison-Wesley Professional, 1998, p. 439. ISBN 978-0-201-30973-7.

- ↑ «Operating Systems and PAE Support» (en anglès). Hardware Developers Center, 01-06-2017. [Consulta: 11 juliol 2023].

- ↑ «PAE - Ubuntu Community Help Wiki» (en anglès).

- ↑ «Appendix E». A: AMD Athlon™ Processor x86 Code Optimization Guide (en anglès). Revision K. AMD, Inc., febrer 2002, p. 250.

- ↑ «AMD Athlon 500 - AMD-K7500MTR51B C» (en anglès). Cpu-world.com, 26-03-2014. [Consulta: 11 juliol 2023].

- ↑ «AMD-762 System Controller» (en anglès).

- ↑ 9,0 9,1 AMD Corporation. «Volume 2: System Programming» (en anglès). AMD64 Architecture Programmer's Manual. AMD Corporation, juny 2023. [Consulta: 11 juliol 2023].

- ↑ 10,0 10,1 10,2 AMD Corporation. «Volume 2: System Programming» (en anglès). AMD64 Architecture Programmer's Manual. AMD Corporation, juny 2023. [Consulta: 11 juliol 2023].

- ↑ «Volume 3 (3A, 3B, 3C & 3D): System Programming Guide» (en anglès). Intel 64 and IA-32 Architectures Software Developer’s Manual. Intel, juny 2023. [Consulta: 11 juliol 2023].

- ↑ Pentium® III Xeon™ Processor at 500 and 550 MHz Datasheet (en anglès). Intel Corporation, p. 86. 245094-002.

- ↑ AMD Corporation. «Volume 2: System Programming» (en anglès). AMD64 Architecture Programmer's Manual. AMD Corporation, juny 2023. [Consulta: 11 juliol 2023].

- ↑ «4.4 Paging». A: Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 3A (en anglès). Intel.

- ↑ AMD Corporation. «Volume 2: System Programming» (en anglès). AMD64 Architecture Programmer's Manual. AMD Corporation, juny 2023. [Consulta: 11 juliol 2023].