CUDA

|

|

Aquest article o secció necessita millorar una traducció deficient. |

| Tipus | General-purpose computing on graphics processing units |

|---|---|

| Versió inicial | 23 juny 2007 |

| Versió estable | 27 febrer 2019 |

| Llicència | Programari de propietat, Programari gratuït |

| Característiques tècniques | |

| Sistema operatiu | Microsoft Windows, Linux, MacOS |

| Equip | |

| Desenvolupador(s) | NVIDIA |

Fonts de codi | |

| Més informació | |

| Lloc web | Nvidia's CUDA zone |

|

| |

CUDA (acrònim de Compute Unified Device Architecture (Arquitectura de còmput de dispositius unificats)) és una plataforma de computació paral·lela i model d'Interfície de programació d'aplicacions (API) creada per Nvidia per permetre a desenvolupadors i enginyers de programari accelerar l'execució dels seus codis fent servir Unitats de processament gràfic (GPU) amb capacitat CUDA per a processament de caràcter general.[1]

La plataforma CUDA és una capa de software que dona accés directe al conjunt virtual d'instruccions de la GPU i als seus elements de comput paral·lel a efectes d'executar nuclis de cómput (CUDA Kernels).[2]

La plataforma va ser desenvolupada amb l'objectiu de treballar conjuntament amb llenguatges de programació com C, C++ i Fortran, tot i que posteriorment ha acabat implementant-se en un ampli espectre de llenguatges de programació com Java, Lua, MATLAB… Aquesta accessibilitat facilita als especialistes de programació paral·lela l'ús dels recursos que ofereix una GPU, en contrast amb altres APIs natives pròpiament de la prográmacio de gráfics (com Direct3D o OpenGL), les quals tenien un enfóc purament gráfic i requerien grans coneixements en aquest ambit.

CUDA dona suport a entorns de treball (Frameworks) orientats a la programació amb acceleradors com OpenACC i OpenCL.

Història

[modifica]La unitat de processament gràfic (GPU), és un processador especialitzat, dirigit en els seus inicis a les demandes de càlcul intensiu de gràfics d'alta resolució en 3D en temps real. A l'any 2012, les GPU havien evolucionat fins haberse convertit en sistemes multi-core masius, altament paral·lels i enfocats a la manipulació eficient de grans blocs de dades. Aquest disseny és més eficaç que la unitat central de processament de propòsit general (CPU) per als algorismes que han de treballar grans blocs de dades i requerint poca interacció.

Aquesta nou paradigma va posar de manifest la gran necessitat d'un llenguatge de programació no orientat estrictament als gràfics que permetés la utilitzar totes les prestacions d'aquests dispositius d'una forma versatil i de relatiu alt nivell, assentant la importancia del llenguatge de programació CUDA present al mercat des de 2007.

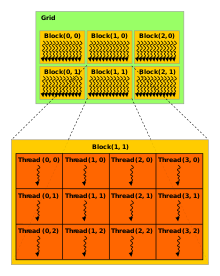

Per l'execució de programes paral·lels a través de kernels CUDA Kernels s'utilitza una jerarquia de fils que conté tres categories anidades: Thread, ThreadBlock i Grid. Aquests estan anidats com mostra imatge dreta, on podem veure: En blau la representació dels threads, englobats en els blocks grisos, dintre d'un grid, representat en verd.

Com aquí s'observa, la quantitat de threads i blocks creats ve definida des de la crida a la funció. La següent imatge, mostra de forma més detallada com després aquests fils s'organitzen, així com una serie d'identificadors associats. Aquests identificadors tenen una traducció directa en variables accesibles del llenguatge, que descriuen el context de treball en termes de dimensions i posició:

CUDA introdueix dos tipus de dades per aquestes descripcions:

- unit3: Vector interconstruït de tipus sencer. Funció constructor: unit3 nom_variable(x,i,z).

- dim3: Vector interconstruït i basat en unit3. Utilitzat per especificar dimensions. Funció constructor: dim3 nom_variable(x,i,z) (qualsevol component no especificat s'inicialitza a 1).

Amb aquest tipus de dades construeix 4 variables, 2 referents a l'identificador de localització i 2 referents a la mida del context:

- ThreadIdx: Variable de tipus unit3 que conté l'índex d'un thread (dins d'un Block).

- BlockIdx: Variables de tipus unit3 que conté l'índex d'un block (dins d'un Grid).

- BlockDim: Variable de tipus dim3 que conté la dimensió d'un Block.

- GridDim: Variable de tipus dim3 que conté la dimensió d'una Grid.

Els fils poden estar organitzats, d'acord amb l'aplicació, en blocs d'una dimensió (per manipular vectors), de dues dimensions (per manipular matrius) i de tres dimensions (per manipular arranjaments tridimensionals).

Els threads de CUDA poden accedir a múltiples memòries durant l'execució que es poden dividir en aquests tres casos:

- Memòria privada per thread d'ús exclusiu

- Memòria per bloc, és visible per tots els threads del bloc i té el mateix temps de vida que el bloc

- Memòria global accessible per tots els threads

Hi ha també dos memòries addicionals optimitzades per diferents usos accessibles per tots els threads:

- Memòria constant

- Memòria de textures i superfícies

Els espais de memòria global, constant i de textura són persistents entre kernels llençats en la mateixa aplicació.

Memòria global

[modifica]La memòria global es troba a la memòria del dispositiu, l'accés és fa a través de transaccions de memòria de 32, 64 o 128 bytes. Aquestes operacions de memòria han d'estar alineades de manera natural: només es poden llegir o escriure a memòria segments de 32, 64 o 128 bytes del dispositiu alineats a la seva mida (és a dir, la primera adreça és un múltiple de la seva mida).

Quan un bloc executa una instrucció que accedeix a la memòria global, converteix els accessos de memòria dels fils dins d'un bloc en una o més d'aquestes transaccions de memòria depenent de la mida de la paraula a la qual s'accedeixi en cada fil i la distribució de les adreces de memòria a través dels fils. En general, com més transaccions siguin necessàries, es transferiran més paraules no utilitzades, a més de les paraules que accedeixen als fils, reduint-ne el rendiment. Per exemple, si es genera una transacció de memòria de 32 bytes per a l'accés de 4 bytes de cada fil, el rendiment es divideix en 8.

Memòria compartida

[modifica]La memòria compartida està ubicada en el xip obtenint un amplada de banda més gran i una latència menor que la memòria local o global.

Per aconseguir una amplada de banda major la memòria compartida es divideix en mòduls de memòria de la mateixa mida anomenats bancs als quals es poden accedir de forma simultània. Qualsevol sol·licitud de lectura o escriptura a memòria feta en N direccions que cauen en N bancs de memòria diferents, és a dir, podran ser atesos simultàniament donant com a resultat una amplada de banda global que és n vegades més alt que l'amplada de banda d'un sol mòdul.

Tanmateix, si dues adreces d'una sol·licitud de memòria cauen al mateix banc de memòria, hi ha un conflicte de banc i l'accés ha de ser serialitzat. El maquinari divideix una sol·licitud de memòria amb conflictes de banc en tantes sol·licituds com sigui necessari, disminuint el rendiment per un factor igual al nombre de sol·licituds de memòria separades. Si el nombre de sol·licituds de memòria separades és n, es diu que la sol·licitud de memòria inicial provoca conflictes de banc en forma de n.

Memòria local

[modifica]L'espai de memòria local resideix en la memòria del dispositiu, de manera que els accessos a la memòria local tenen la mateixa latència i amplada de banda baixos que els accessos de memòria global i estan subjectes als mateixos requisits de coalescència de memòria que es descriu als accessos de memòria del dispositiu. No obstant això, la memòria local s'organitza de manera que s'accedeix a paraules de 32 bits consecutives mitjançant identificacions de fil consecutives. Per tant, els accessos s'integraran íntegrament sempre que tots els fils d'un warp accedeixin a la mateixa adreça relativa (per exemple, el mateix índex en una variable de matriu, el mateix membre en una variable d'estructura).

Memòria de textures i superfícies

[modifica]Els espais de memòria per textures i superfícies resideixen en la memòria del dispositiu. El cache de textura està optimitzada per a localitats espacials 2D, cada thread del mateix bloc que llegeix una textura o superfície aconsegueixin un millor rendiment.

Estructura d'una aplicació CUDA

[modifica]Les aplicacions en CUDA estan pensades per executar codi en forma vectorial aprofitant l'explotació del paral·lelisme al màxim. Una aplicació CUDA pot estar composta per parts de codi C seqüencials executades en CPU i kernels paral·lels executats en GPU combinant les dues infraestructures.

#include <cuda.h>

void vecAdd(float* A, float* B, float* C, int n)

{

int size = n* sizeof(float);

float* A_d, B_d, C_d;

…

1. Reservem en la memoria del dispositus els arrays A, B i C

cudaMalloc((void **) &A_d, size);

cudaMalloc((void **) &B_d, size);

cudaMalloc((void **) &C_d, size);

// Copiem A i B a la memoria del dispositiu

cudaMemcpy(A_d, A, size, cudaMemcpyHostToDevice);

cudaMemcpy(B_d, B, size, cudaMemcpyHostToDevice);

2. // Executem el kernel de codi en el dispositiu per tal d'executar la suma de vectors

3. // Copiem el resultat de C del dispositiu al host (CPU)

cudaMemcpy(C, C_d, size, cudaMemcpyDeviceToHost);

// Lliurem la memoria utilitzada al dispositiu

cudaFree(A_d); cudaFree(B_d); cudaFree (C_d);

}

Per tal de fer les operacions dites anteriorment comptem amb les següents funcions implementades en la llibreria "cuda.h":

- cudaMalloc(Direcció del punter, Mida en bytes): Per reservar memòria al dispositiu.

- cudaFree(Punter a les dades): Per alliberar memòria prèviament reservada.

- cudaMemcpy(Punter de destí, Punter d'origen, Mida en bytes, Direcció de la transferència): Copia de blocs d'informació d'un punter a un altre.

- cudaMemset(Punter, valor, Mida en bytes): Inicialitza una quantitat de bytes a un valor concret.

La direcció de les dades per la funció cudaMemcpy pot ser una de les següents constants:

- cudaMemcpyHostToHost: Copia dades de memòria principal a memòria principal.

- cudaMemcpyHostToDevice : Copia dades de memòria principal a la memòria del dispositiu.

- cudaMemcpyDeviceToHost : Copia dades del dispositiu a memòria principal.

- cudaMemcpyDeviceToDevice : Copia dades del dispositiu al dispositiu.

- cudaMemcpyDefault: Es basa en els punters per decidir a on es copien les dades.

Creació de kernels en CUDA

[modifica]CUDA Kernel CUDA incorpora un nou model d'execució diferent al model seqüencial de les computadores tradicionals. A CUDA, el codi serà executat per múltiples fils d'execció a la vegada (centenars o milers). La programació ha de ser modelada segons la jerarquia de fils d'execució.[7]

Una funció kernel ha de ser invocada per la CPU (host), però s'executa exclusivament en GPU.

Els kernels tenen dues característiques fonamentals:

- Els kernels no poden retornar un valor de forma explícita. Els resultats han de ser desats sobre estructures de dades que s'hagin enviat a la funció en el moment de la crida.

- Els kernels generen de forma explícita la jerarquia de fils d'execció quan es realitza la crida segons el nombre de blocs de fils d'execució i el nombre de fils d'execució per bloc. Així doncs, una mateixa funció CUDA pot ser cridada diverses vegades en un mateix codi, i tenir una jerarquia de fils d'execució diferents segons la crida.

// Declaració del kernel CUDA.

__global__ void foo(double *vector,int limit)

{

// Calcular l'identificador del thread

int identificador = blockIdx.x*blockDim.x + threadIdx.x;

// Comprovar que estem dintre del rang del vector

if (identificador < limit)

vector[identificador] = 0;

}

Invocacions a un kernel

[modifica]Una vegada declarada la funció, és recomanable declarar variables per a gestionar la jerarquia de fils d'execució.

int CTA_NUM = (N + 1023)/1024;

dim3 blocks(CTA_NUM, 1, 1);

dim3 threadsPerBlock (1024, 1, 1);

Finalment, es realitza la crida al kernel

foo<<< blocks, threadsPerBlock >>>(d_vector_in, d_vector_out, N);

Exemple

[modifica]Codi d'exemple: Suma de vectors

#include <stdio.h>

#include <stdlib.h>

#include <math.h>

// Declaració del kernel CUDA.

__global__ void sumaVectors(double *a, double *b, double *c, int n)

{

// Calcular l'identificador del thread

int id = blockIdx.x*blockDim.x+threadIdx.x;

// Comprobar que estem dintre del rang del vector

if (id < n)

c[id] = a[id] + b[id];

}

// Funció principal

int main(int argc, char* argv[])

{

// Mida del vector

int n = 1024*1024;

// Declarem els punters d'entrada per la memòria del host

double *host_vector_a;

double *host_vector_b;

// Declarem els punters de sortida per la memòria del host

double *host_vector_c;

// Declarem els punters d'entrada per la memòria del dispositiu (GPU)

double *device_vector_a;

double *device_vector_b;

// Declarem els punters de sortida per la memòria del dispositiu (GPU)

double *device_vector_c;

// Calculem la mida del vector en bytes

size_t bytes = n*sizeof(double);

// Reservar memòria a l'espai del host per als vectors

host_vector_a = (double*)malloc(bytes);

host_vector_b = (double*)malloc(bytes);

host_vector_c = (double*)malloc(bytes);

// Reservar memòria a l'espai del dispositiu (GPU) per als vectors

cudaMalloc(&device_vector_a, bytes);

cudaMalloc(&device_vector_b, bytes);

cudaMalloc(&device_vector_c, bytes);

int i;

// Inicialitzar valors del vectors

for(i = 0; i < n; i++) {

host_vector_a[i] = sin(i)*sin(i);

host_vector_b[i] = cos(i)*cos(i);

}

// Copiar els vectors del host al dispositiu (D <-- H)

cudaMemcpy(device_vector_a, host_vector_a, bytes, cudaMemcpyHostToDevice);

cudaMemcpy(device_vector_b, host_vector_b, bytes, cudaMemcpyHostToDevice);

int blockSize, gridSize;

// Nombre de threads per bloc

blockSize = 1024;

// Nombre de blocks al grid

gridSize = (int)ceil((float)n/blockSize);

// Executem el kernel

sumaVectors<<<gridSize, blockSize>>>(device_vector_a, device_vector_b, device_vector_c, n);

// Copiem el vector de sortida del dispositiu al host (H <-- D)

cudaMemcpy(host_vector_c, device_vector_c, bytes, cudaMemcpyDeviceToHost);

// Calculem el resultat final

double sum = 0;

for(i=0; i<n; i++)

sum += host_vector_c[i];

printf("final result: %f\n", sum/n);

// Alliberem la memòria del dispositiu

cudaFree(device_vector_a);

cudaFree(device_vector_b);

cudaFree(device_vector_c);

// Alliberem la memòria del host

free(host_vector_a);

free(host_vector_b);

free(host_vector_c);

return 0;

}

Codi exemple: Multiplicació per 2 de tots els pixels en una determinada zona

__global__ void PictureKernel(float* d_Pin, float* d_Pout, int n,int m)

{

// Calculem la fila de d_Pin i d_Pout que estem processant.

int Row = blockIdx.y*blockDim.y + threadIdx.y;

// Calculem la columna de d_Pin i d_Pout que estem processant.

int Col = blockIdx.x*blockDim.x + threadIdx.x;

// Cada thread computarà 1 element de d_Pin generant el corresponent d_Pout

if ((Row < m) && (Col < n)) {

d_Pout[Row*n+Col] = 2*d_Pin[Row*n+Col];

}

}

Com els diferents fils col·laboren entre ells i poden compartir dades, es requereixen unes directives de sincronització. En un kernel, es pot declarar una barrera afegint una crida a __syncthreads(), amb això tots els fils s'esperaran fins que tots els fils arribin al mateix punt.

Característiques i especificacions de les diferents versió

[modifica]| Compatibilitat amb funcions (les funcions no llistades són compatibles amb totes les capacitats de computació) | Capacitat de computació (versió) | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1.0 | 1.1 | 1.2 | 1.3 | 2.x | 3.0 | 3.2 | 3.5, 3.7, 5.0, 5.2 | 5.3 | 6.x | 7.x | |||

| Funcions atòmiques senceres que operen en paraules de 32 bits a la memòria global | No | Sí | |||||||||||

| atomicExch () que opera en valors de punt flotant de 32 bits en la memòria global | |||||||||||||

| Funcions atòmiques senceres que operen en paraules de 32 bits en memòria compartida | No | Sí | |||||||||||

| atomicExch () que opera en valors de punt flotant de 32 bits en memòria compartida | |||||||||||||

| Funcions atòmiques senceres que operen en paraules de 64 bits a la memòria global | |||||||||||||

| Funcions de vot de warp | |||||||||||||

| Operacions de punt flotant de doble precisió | No | Sí | |||||||||||

| Funcions atòmiques que operen en valors enters de 64 bits a la memòria compartida | No | Sí | |||||||||||

| Addició atòmica de punt flotant que opera en paraules de 32 bits en memòria global i compartida | |||||||||||||

| _ballot() | |||||||||||||

| _threadfence_system() | |||||||||||||

| _syncthreads_count(), _syncthreads_and(), _syncthreads_or() | |||||||||||||

| Funcions de superfície | |||||||||||||

| Graella 3D del bloc de fils | |||||||||||||

| Funcions de shuffle warp | No | Sí | |||||||||||

| Funnel shift | No | Sí | |||||||||||

| Paral·lelisme dinàmic | No | Sí | |||||||||||

| Operacions de punt flotant de mitja precisió:

addició, resta, multiplicació, comparació, funcions de shuffle de l'ordit, conversió |

No | Sí | |||||||||||

| Addició atòmica operant en valors de punt flotant de 64 bits en memòria global i memòria compartida | No | Sí | |||||||||||

| Tensor core | No | Sí | |||||||||||

| Tipus de dada | Operació | Suportat des de | Compatible des de

per a la memòria global |

Compatible des de

per a la memòria compartida |

|---|---|---|---|---|

| Enter de 16-bit | operacions generals | |||

| Enter de 32-bit | funcions atòmiques | 1.1 | 1.2 | |

| Enter de 64-bit | funcions atòmiques | 1.2 | 2.0 | |

| Punt flotant de 16 bits | suma, resta,

multiplicació, comparació, funcions de shuffle de l'ordit, conversió |

5.3 | ||

| Punt flotant de 32 bits | atomicExch() | 1.1 | 1.2 | |

| Punt flotant de 32 bits | suma atòmica | 2.0 | 2.0 | |

| Punt flotant de 64 bits | operacions generals | 1.3 | ||

| Punt flotant de 64 bits | suma atòmica | 6.0 | 6.0 | |

| Nuclis tensor | 7.0 |

Nota: Totes les línies que falten o les entrades buides reflecteixen alguna falta d'informació sobre aquest article exacte..

[10]

| Especificacions tècniques | Capacitat de computació (versió) | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1.0 | 1.1 | 1.2 | 1.3 | 2.x | 3.0 | 3.2 | 3.5 | 3.7 | 5.0 | 5.2 | 5.3 | 6.0 | 6.1 | 6.2 | 7.0 (7.2?) |

7.5 | ||

| Nombre màxim de xarxes de residents per dispositiu

(execució concurrent del nucli) |

t.b.d. | 16 | 4 | 32 | 16 | 128 | 32 | 16 | 128 | |||||||||

| Màxima dimensionalitat de la graella de blocs de fils | 2 | 3 | ||||||||||||||||

| Dimensió x màxima d'una quadrícula de blocs de fils | 65535 | 231 − 1 | ||||||||||||||||

| Màxima dimensió y, o z d'una quadrícula de blocs de fils | 65535 | |||||||||||||||||

| Màxima dimensionalitat del bloc de fils | 3 | |||||||||||||||||

| Màxima dimensió x o y d'un bloc | 512 | 1024 | ||||||||||||||||

| Dimensió z màxima d'un bloc | 64 | |||||||||||||||||

| Nombre màxim de fils per bloc | 512 | 1024 | ||||||||||||||||

| Mida del Warp | 32 | |||||||||||||||||

| Nombre màxim de blocs residents per multiprocessador | 8 | 16 | 32 | 16 | ||||||||||||||

| Nombre màxim de warps residents per multiprocessador | 24 | 32 | 48 | 64 | 32 | |||||||||||||

| Nombre màxim de fils residents per multiprocessador | 768 | 1024 | 1536 | 2048 | 1024 | |||||||||||||

| Nombre de registres de 32 bits per multiprocessador | 8 K | 16 K | 32 K | 64 K | 128 K | 64 K | ||||||||||||

| Nombre màxim de registres de 32 bits per bloc de fils | N/A | 32 K | 64 K | 32 K | 64 K | 32 K | 64 K | 32 K | 64 K | |||||||||

| Nombre màxim de registres de 32 bits per fil | 124 | 63 | 255 | |||||||||||||||

| Quantitat màxima de memòria compartida per multiprocessador | 16 KB | 48 KB | 112 KB | 64 KB | 96 KB | 64 KB | 96 KB | 64 KB | 96 KB (of 128) |

64 KB (of 96) | ||||||||

| Quantitat màxima de memòria compartida per bloc de fils | 48 KB | 48/96 KB | 64 KB | |||||||||||||||

| Nombre de bancs de memòria compartida | 16 | 32 | ||||||||||||||||

| Quantitat de memòria local per fil | 16 KB | 512 KB | ||||||||||||||||

| Mida de memòria constant | 64 KB | |||||||||||||||||

| Treball de memòria cau establert per multiprocessador per a una memòria constant | 8 KB | 4 KB | 8 KB | |||||||||||||||

| Treball de memòria cau establert per multiprocessador per a memòria de textura | 6 – 8 KB | 12 KB | 12 – 48 KB | 24 KB | 48 KB | N/A | 24 KB | 48 KB | 24 KB | 32 – 128 KB | 32 – 64 KB | |||||||

| Amplada màxima per a una referència de textura 1D lligada a una CUDA matriu | 8192 | 65536 | ||||||||||||||||

| Amplada màxima per a la referència de textura 1D lligada a la memòria lineal | 227 | |||||||||||||||||

| Amplada màxima i nombre de capes per a una referència de textura en capes 1D | 8192 × 512 | 16384 × 2048 | ||||||||||||||||

| Amplada i alçada màximes per a la referència de textura 2D lligada a una matriu CUDA | 65536 × 32768 | 65536 × 65535 | ||||||||||||||||

| Amplada i alçada màximes per a la referència de textura 2D lligada a una memòria lineal | 65000² | |||||||||||||||||

| L'amplada i l'altura màximes per a la referència de textura 2D lligades a una textura de suport de matriu CUDA es recullen | N/A | 16384² | ||||||||||||||||

| Amplada, alçada i nombre màxim de capes per a una referència de text en capes 2D | 8192 × 8192 × 512 | 16384 × 16384 × 2048 | ||||||||||||||||

| Amplada, alçada i profunditat màximes per a una referència de textura 3D lligada a la memòria lineal o una matriu CUDA | 20483 | 40963 | ||||||||||||||||

| Amplada màxima i nombre de capes per a una referència de textura en capes de cubemap | N/A | 16384 × 2046 | ||||||||||||||||

| Nombre màxim de textures que es poden enllaçar amb un nucli | 128 | 256 | ||||||||||||||||

| Amplada màxima per a una referència de superfície 1D lligada a una matriu CUDA | No | 65536 | ||||||||||||||||

| Amplada màxima i nombre de capes per a una referència de superfície en capes 1D | 65536 × 2048 | |||||||||||||||||

| Amplada i alçada màximes per a una referència de superfície 2D lligada a una matriu CUDA | 65536 × 32768 | |||||||||||||||||

| Amplada, alçada i nombre màxim de capes per a una referència de superfície en capes 2D | 65536 × 32768 × 2048 | |||||||||||||||||

| Amplada, alçada i profunditat màxima per a una referència de superfície 3D lligada a una matriu CUDA | 65536 × 32768 × 2048 | |||||||||||||||||

| Amplada màxima i nombre de capes per a una referència de superfície en capes cubemap | 32768 × 2046 | |||||||||||||||||

| Nombre màxim de superfícies que es poden unir a un nucli |

8 | 16 | ||||||||||||||||

| Nombre màxim d'instruccions per n | 2 million | 512 million | ||||||||||||||||

| Especificacions d'arquitectura | Capacitat de computació (versió) | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1.0 | 1.1 | 1.2 | 1.3 | 2.0 | 2.1 | 3.0 | 3.5 | 3.7 | 5.0 | 5.2 | 6.0 | 6.1, 6.2 | 7.0, 7.2 | 7.5 | |

| Nombre de carrils ALU per a operacions aritmètiques de punt flotant sencer i de precisió | 8[12] | 32 | 48 | 192 | 128 | 64 | 128 | 64 | |||||||

| Nombre d'unitats de funcions especials per a funcions transcendents de punt flotant de precisió única | 2 | 4 | 8 | 32 | 16 | 32 | 16 | ||||||||

| Nombre d'unitats de filtratge de textures per a cada unitat d'adreça de textura o unitat de sortida de representació (ROP) | 2 | 4 | 8 | 16 | 8[13] | ||||||||||

| Nombre de planificadors de warp | 1 | 2 | 4 | 2 | 4 | ||||||||||

| Nombre màxim d'instruccions emeses alhora per un sol planificador | 1 | 2[14] | 1 | ||||||||||||

| Nombre de nuclis de tensor | N/A | 8[13] | |||||||||||||

| Mida en KB de memòria unificada per a memòria cau de dades i memòria compartida per multi processador | t.b.d. | 128 | 96[15] | ||||||||||||

Per obtenir més informació, vegeu l'article: «NVIDIA CUDA Compute Capability Comparative Table». and read Nvidia CUDA programming guide.[17]

Tarjetes Suportades

[modifica]Nivell de CUDA soportat per la tarjeta GPU. Vegeu també a: Nvidia:

- CUDA SDK 1.0 suport per capacitat de cómput 1.0 – 1.1 (Tesla)[18]

- CUDA SDK 1.1 suport per capacitat de cómput 1.0 – 1.1+x (Tesla)

- CUDA SDK 2.0 suport per capacitat de cómput 1.0 – 1.1+x (Tesla)

- CUDA SDK 2.1 – 2.3.1suport per capacitat de cómput 1.0 – 1.3 (Tesla)[19][20][21][22]

- CUDA SDK 3.0 – 3.1 suport per capacitat de cómput 1.0 – 2.0 (Tesla, Fermi)[23][24]

- CUDA SDK 3.2 suport per capacitat de cómput 1.0 – 2.1 (Tesla, Fermi)[25]

- CUDA SDK 4.0 – 4.2 suport per capacitat de cómput 1.0 – 2.1+x (Tesla, Fermi, more?)

- CUDA SDK 5.0 – 5.5 suport per capacitat de cómput 1.0 – 2.1+x (Tesla, Fermi, more?)

- CUDA SDK 6.0 suport per capacitat de cómput 1.0 – 3.5 (Tesla, Fermi, Kepler)

- CUDA SDK 6.5 suport per capacitat de cómput 1.1 – 5.x (Tesla, Fermi, Kepler, Maxwell). Last version with support for compute capability 1.x (Tesla)

- CUDA SDK 7.0 – 7.5 suport per capacitat de cómput 2.0 – 5.x (Fermi, Kepler, Maxwell)

- CUDA SDK 8.0 suport per capacitat de cómput 2.0 – 6.x (Fermi, Kepler, Maxwell, Pascal). Last version with support for compute capability 2.x (Fermi)

- CUDA SDK 9.0 – 9.2 suport per capacitat de cómput 3.0 – 7.2 (Kepler, Maxwell, Pascal, Volta)

- CUDA SDK 10.0 – 10.1 suport per capacitat de cómput 3.0 – 7.5 (Kepler, Maxwell, Pascal, Volta, Turing)

| Compute capability (version) |

Micro- architecture |

GPUs | GeForce | Quadro, NVS | Tesla | Tegra, Jetson, DRIVE |

|---|---|---|---|---|---|---|

| 1.0 | Tesla | G80 | GeForce 8800 Ultra, GeForce 8800 GTX, GeForce 8800 GTS(G80) | Quadro FX 5600, Quadro FX 4600, Quadro Plex 2100 S4 | Tesla C870, Tesla D870, Tesla S870 | |

| 1.1 | G92, G94, G96, G98, G84, G86 | GeForce GTS 250, GeForce 9800 GX2, GeForce 9800 GTX, GeForce 9800 GT, GeForce 8800 GTS(G92), GeForce 8800 GT, GeForce 9600 GT, GeForce 9500 GT, GeForce 9400 GT, GeForce 8600 GTS, GeForce 8600 GT, GeForce 8500 GT, GeForce G110M, GeForce 9300M GS, GeForce 9200M GS, GeForce 9100M G, GeForce 8400M GT, GeForce G105M |

Quadro FX 4700 X2, Quadro FX 3700, Quadro FX 1800, Quadro FX 1700, Quadro FX 580, Quadro FX 570, Quadro FX 470, Quadro FX 380, Quadro FX 370, Quadro FX 370 Low Profile, Quadro NVS 450, Quadro NVS 420, Quadro NVS 290, Quadro NVS 295, Quadro Plex 2100 D4, Quadro FX 3800M, Quadro FX 3700M, Quadro FX 3600M, Quadro FX 2800M, Quadro FX 2700M, Quadro FX 1700M, Quadro FX 1600M, Quadro FX 770M, Quadro FX 570M, Quadro FX 370M, Quadro FX 360M, Quadro NVS 320M, Quadro NVS 160M, Quadro NVS 150M, Quadro NVS 140M, Quadro NVS 135M, Quadro NVS 130M, Quadro NVS 450, Quadro NVS 420,[27] Quadro NVS 295 |

|||

| 1.2 | GT218, GT216, GT215 | GeForce GT 340*, GeForce GT 330*, GeForce GT 320*, GeForce 315*, GeForce 310*, GeForce GT 240, GeForce GT 220, GeForce 210, GeForce GTS 360M, GeForce GTS 350M, GeForce GT 335M, GeForce GT 330M, GeForce GT 325M, GeForce GT 240M, GeForce G210M, GeForce 310M, GeForce 305M |

Quadro FX 380 Low Profile, Nvidia NVS 300, Quadro FX 1800M, Quadro FX 880M, Quadro FX 380M, Nvidia NVS 300, NVS 5100M, NVS 3100M, NVS 2100M, ION | |||

| 1.3 | GT200, GT200b | GeForce GTX 295, GTX 285, GTX 280, GeForce GTX 275, GeForce GTX 260 | Quadro FX 5800, Quadro FX 4800, Quadro FX 4800 for Mac, Quadro FX 3800, Quadro CX, Quadro Plex 2200 D2 | Tesla C1060, Tesla S1070, Tesla M1060 | ||

| 2.0 | Fermi | GF100, GF110 | GeForce GTX 590, GeForce GTX 580, GeForce GTX 570, GeForce GTX 480, GeForce GTX 470, GeForce GTX 465, GeForce GTX 480M | Quadro 6000, Quadro 5000, Quadro 4000, Quadro 4000 for Mac, Quadro Plex 7000, Quadro 5010M, Quadro 5000M | Tesla C2075, Tesla C2050/C2070, Tesla M2050/M2070/M2075/M2090 | |

| 2.1 | GF104, GF106 GF108, GF114, GF116, GF117, GF119 | GeForce GTX 560 Ti, GeForce GTX 550 Ti, GeForce GTX 460, GeForce GTS 450, GeForce GTS 450*, GeForce GT 640 (GDDR3), GeForce GT 630, GeForce GT 620, GeForce GT 610, GeForce GT 520, GeForce GT 440, GeForce GT 440*, GeForce GT 430, GeForce GT 430*, GeForce GT 420*, GeForce GTX 675M, GeForce GTX 670M, GeForce GT 635M, GeForce GT 630M, GeForce GT 625M, GeForce GT 720M, GeForce GT 620M, GeForce 710M, GeForce 610M, GeForce 820M, GeForce GTX 580M, GeForce GTX 570M, GeForce GTX 560M, GeForce GT 555M, GeForce GT 550M, GeForce GT 540M, GeForce GT 525M, GeForce GT 520MX, GeForce GT 520M, GeForce GTX 485M, GeForce GTX 470M, GeForce GTX 460M, GeForce GT 445M, GeForce GT 435M, GeForce GT 420M, GeForce GT 415M, GeForce 710M, GeForce 410M |

Quadro 2000, Quadro 2000D, Quadro 600, Quadro 4000M, Quadro 3000M, Quadro 2000M, Quadro 1000M, NVS 310, NVS 315, NVS 5400M, NVS 5200M, NVS 4200M | |||

| 3.0 | Kepler | GK104, GK106, GK107 | GeForce GTX 770, GeForce GTX 760, GeForce GT 740, GeForce GTX 690, GeForce GTX 680, GeForce GTX 670, GeForce GTX 660 Ti, GeForce GTX 660, GeForce GTX 650 Ti BOOST, GeForce GTX 650 Ti, GeForce GTX 650, GeForce GTX 880M, GeForce GTX 780M, GeForce GTX 770M, GeForce GTX 765M, GeForce GTX 760M, GeForce GTX 680MX, GeForce GTX 680M, GeForce GTX 675MX, GeForce GTX 670MX, GeForce GTX 660M, GeForce GT 750M, GeForce GT 650M, GeForce GT 745M, GeForce GT 645M, GeForce GT 740M, GeForce GT 730M, GeForce GT 640M, GeForce GT 640M LE, GeForce GT 735M, GeForce GT 730M |

Quadro K5000, Quadro K4200, Quadro K4000, Quadro K2000, Quadro K2000D, Quadro K600, Quadro K420, Quadro K500M, Quadro K510M, Quadro K610M, Quadro K1000M, Quadro K2000M, Quadro K1100M, Quadro K2100M, Quadro K3000M, Quadro K3100M, Quadro K4000M, Quadro K5000M, Quadro K4100M, Quadro K5100M, NVS 510, Quadro 410 | Tesla K10, GRID K340, GRID K520 | |

| 3.2 | GK20A | Tegra K1, Jetson TK1 | ||||

| 3.5 | GK110, GK208 | GeForce GTX Titan Z, GeForce GTX Titan Black, GeForce GTX Titan, GeForce GTX 780 Ti, GeForce GTX 780, GeForce GT 640 (GDDR5), GeForce GT 630 v2, GeForce GT 730, GeForce GT 720, GeForce GT 710, GeForce GT 740M (64-bit, DDR3), GeForce GT 920M | Quadro K6000, Quadro K5200 | Tesla K40, Tesla K20x, Tesla K20 | ||

| 3.7 | GK210 | Tesla K80 | ||||

| 5.0 | Maxwell | GM107, GM108 | GeForce GTX 750 Ti, GeForce GTX 750, GeForce GTX 960M, GeForce GTX 950M, GeForce 940M, GeForce 930M, GeForce GTX 860M, GeForce GTX 850M, GeForce 845M, GeForce 840M, GeForce 830M, GeForce GTX 870M | Quadro K1200, Quadro K2200, Quadro K620, Quadro M2000M, Quadro M1000M, Quadro M600M, Quadro K620M, NVS 810 | Tesla M10 | |

| 5.2 | GM200, GM204, GM206 | GeForce GTX Titan X, GeForce GTX 980 Ti, GeForce GTX 980, GeForce GTX 970, GeForce GTX 960, GeForce GTX 950, GeForce GTX 750 SE, GeForce GTX 980M, GeForce GTX 970M, GeForce GTX 965M | Quadro M6000 24GB, Quadro M6000, Quadro M5000, Quadro M4000, Quadro M2000, Quadro M5500, Quadro M5000M, Quadro M4000M, Quadro M3000M | Tesla M4, Tesla M40, Tesla M6, Tesla M60 | ||

| 5.3 | GM20B | Tegra X1, Jetson TX1, Jetson Nano, DRIVE CX, DRIVE PX | ||||

| 6.0 | Pascal | GP100 | Quadro GP100 | Tesla P100 | ||

| 6.1 | GP102, GP104, GP106, GP107, GP108 | Nvidia TITAN Xp, Titan X, GeForce GTX 1080 Ti, GTX 1080, GTX 1070 Ti, GTX 1070, GTX 1060, GTX 1050 Ti, GTX 1050, GT 1030, MX150 | Quadro P6000, Quadro P5000, Quadro P4000, Quadro P2000, Quadro P1000, Quadro P600, Quadro P400, Quadro P5000(Mobile), Quadro P4000(Mobile), Quadro P3000(Mobile) | Tesla P40, Tesla P6, Tesla P4 | ||

| 6.2 | GP10B[28] | Tegra X2, Jetson TX2, DRIVE PX 2 | ||||

| 7.0 | Volta | GV100 | NVIDIA TITAN V | Quadro GV100 | Tesla V100 | |

| 7.2 | GV10B[29] | Tegra Xavier, Jetson AGX Xavier, DRIVE AGX Xavier, DRIVE AGX Pegasus | ||||

| 7.5 | Turing | TU102, TU104, TU106, TU116, TU117 | NVIDIA TITAN RTX, GeForce RTX 2080 Ti, RTX 2080, RTX 2070, RTX 2060, GTX 1660 Ti, GTX 1660, GTX 1650 | Quadro RTX 8000, Quadro RTX 6000, Quadro RTX 5000, Quadro RTX 4000, Quadro T2000, Quadro T1000 | Tesla T4 | |

| 8.0 |

'*' – OEM - Només productes.

Llibreries per llenguatges específics

[modifica]- Common Lisp – cl-cuda

- Clojure – ClojureCUDA

- Fortran – FORTRAN CUDA Arxivat 2012-04-10 a Wayback Machine., PGI CUDA Fortran Compiler

- F# – Alea.CUDA

- Haskell – Data.Array.Accelerate

- IDL – GPULib Arxivat 2012-11-07 a Wayback Machine.

- Java – jCUDA, JCuda, JCublas, JCufft, CUDA4J

- Julia – CUDAnative.jl Arxivat 2019-05-05 a Wayback Machine.[30]

- Lua – KappaCUDA

- Mathematica – CUDALink

- MATLAB – Parallel Computing Toolbox, MATLAB Distributed Computing Server,[31] and 3rd party packages like Jacket.

- .NET – CUDA.NET, Managed CUDA, CUDAfy.NET .NET kernel and host code, CURAND, CUBLAS, CUFFT

- Perl – KappaCUDA, CUDA::Minimal, AI::MXNet::CudaKernel

- Python – Numba, NumbaPro, PyCUDA, KappaCUDA, Theano Arxivat 2020-11-08 a Wayback Machine.

- Ruby – KappaCUDA (Broken link)

- R – gpuRcuda

Referències

[modifica]- ↑ «Cuda ZONE - CUDA. NVIDIA Corporation» (en anglés). NVIDIA Corporation.

- ↑ «CUDA Kernel programming guide - CUDA. NVIDIA Corporation» (en anglés).

- ↑ «CUDA Programing Guide - Thread Hierarchy» (en anglès). NVIDIA.

- ↑ «Understanding the basics of CUDA Thread Hierarchies» (en anglès), 12-03-2018. Arxivat de l'original el 2019-04-22. [Consulta: 22 abril 2019].

- ↑ «Jerarquia de memòria».

- ↑ «CUDA C Programming Guide» (en anglès). [Consulta: 28 març 2019].

- ↑ «CUDA kernel».

- ↑ «Sincronització CUDA». Arxivat de l'original el 2017-05-10. [Consulta: 24 maig 2017].

- ↑ «H.1. Features and Technical Specifications – Table 13. Feature Support per Compute Capability» (en anglès).

- ↑ https://docs.nvidia.com/cuda/cuda-c-programming-guide/index.html#features-and-technical-specifications

- ↑ H.1. Features and Technical Specifications – Table 14. Technical Specifications per Compute Capability

- ↑ ALUs perform only single-precision floating-point arithmetics. There is 1 double-precision floating-point unit.

- ↑ 13,0 13,1 ; Giroux, Olivier; Harris, Mark; Stam, Nick«Inside Volta: The World's Most Advanced Data Center GPU», 10-05-2017.

- ↑ No more than one scheduler can issue 2 instructions at once. The first scheduler is in charge of warps with odd IDs. The second scheduler is in charge of warps with even IDs.

- ↑ «H.6.1. Architecture» (en anglès).

- ↑ «H.6. Compute Capability 7.x» (en anglès).

- ↑ «Appendix F. Features and Technical Specifications». (3.2 MiB), page 148 of 175 (Version 5.0 octubre 2012).

- ↑ http://developer.download.nvidia.com/compute/cuda/1.0/NVIDIA_CUDA_Programming_Guide_1.0.pdf

- ↑ http://developer.download.nvidia.com/compute/cuda/2_1/toolkit/docs/NVIDIA_CUDA_Programming_Guide_2.1.pdf

- ↑ http://developer.download.nvidia.com/compute/cuda/2_2/toolkit/docs/NVIDIA_CUDA_Programming_Guide_2.2.pdf

- ↑ http://developer.download.nvidia.com/compute/cuda/2_21/toolkit/docs/NVIDIA_CUDA_Programming_Guide_2.2.1.pdf

- ↑ http://developer.download.nvidia.com/compute/cuda/2_3/toolkit/docs/NVIDIA_CUDA_Programming_Guide_2.3.pdf

- ↑ http://developer.download.nvidia.com/compute/cuda/3_0/toolkit/docs/NVIDIA_CUDA_ProgrammingGuide.pdf

- ↑ http://developer.download.nvidia.com/compute/cuda/3_1/toolkit/docs/NVIDIA_CUDA_C_ProgrammingGuide_3.1.pdf

- ↑ http://developer.download.nvidia.com/compute/cuda/3_2_prod/toolkit/docs/CUDA_C_Programming_Guide.pdf

- ↑ https://developer.nvidia.com/cuda-toolkit-archive

- ↑ https://www.techpowerup.com/gpu-specs/quadro-nvs-420.c1448

- ↑ Larabel, Michael. «NVIDIA Rolls Out Tegra X2 GPU Support In Nouveau». Phoronix, 29-03-2017.

- ↑ Nvidia Xavier Specs on TechPowerUp (preliminary)

- ↑ https://devblogs.nvidia.com/gpu-computing-julia-programming-language/

- ↑ «MATLAB Adds GPGPU Support», 20-09-2010. Arxivat de l'original el 2010-09-27.