Pipeline stall

| Model TCP/IP per capes |

|---|

| Xarxes informàtiques |

En el disseny de processadors informàtics canalitzats, una parada de canalització és un retard en l'execució d'una instrucció per resoldre un perill.[1]

Detalls[modifica]

En un pipeline estàndard de cinc etapes, durant l'etapa de descodificació, la unitat de control determinarà si la instrucció descodificada llegeix d'un registre al qual escriu la instrucció executada actualment. Si aquesta condició es compleix, la unitat de control aturarà la instrucció en un cicle de rellotge. També atura la instrucció en l'etapa d'obtenció, per evitar que la instrucció d'aquesta fase sigui sobreescrita per la següent instrucció del programa.[2]

En una arquitectura Von Neumann que utilitza el registre del comptador de programes (PC) per determinar la instrucció actual que s'obté en el pipeline, per evitar que s'obtinguin noves instruccions quan s'ha aturat una instrucció en l'etapa de descodificació, el valor del registre de l'ordinador i es conserven les instruccions de l'etapa de recuperació per evitar canvis. Els valors es conserven fins que la instrucció que causa el conflicte ha passat per l'etapa d'execució. Aquest esdeveniment sovint s'anomena bombolla, per analogia amb una bombolla d'aire en una canonada de fluid.[3]

En algunes arquitectures, l'etapa d'execució de la canalització sempre ha d'estar realitzant una acció a cada cicle. En aquest cas, la bombolla s'implementa alimentant instruccions NOP ("sense operació") a l'etapa d'execució, fins que la bombolla s'aboca.[4]

Exemples[modifica]

Cronologia[modifica]

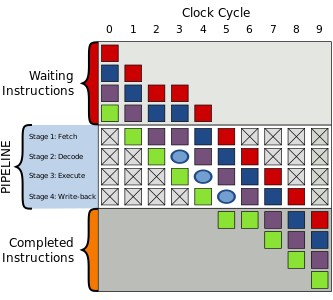

A continuació es mostren dues execucions de les mateixes quatre instruccions a través d'una canalització de 4 etapes, però, per qualsevol motiu, un retard en l'obtenció de la instrucció violeta al cicle #2 fa que es creï una bombolla que retardi també totes les instruccions posteriors.

</img> </img>

|

</img> </img>

|

Canalització RISC clàssic[modifica]

L'exemple següent mostra una bombolla que s'insereix en un pipeline RISC clàssic, amb cinc etapes (IF = Instruction Fetch, ID = Instruction Decode, EX = Execute, MEM = Memory Access, WB = Register write back). En aquest exemple, les dades disponibles després de l'etapa MEM (4a etapa) de la primera instrucció són necessàries com a entrada per l'etapa EX (3a etapa) de la segona instrucció. Sense bombolla, l'etapa EX (3a etapa) només té accés a la sortida de l'etapa EX anterior. Així, afegir una bombolla resol la dependència del temps sense necessitat de propagar les dades cap enrere en el temps (cosa impossible).

| Passant enrere en el temps | Problema resolt amb una bombolla |

</img> </img>

|

</img> </img>

|

Referències[modifica]

- ↑ «CS 441 Lecture» (en anglès). [Consulta: 13 novembre 2023].

- ↑ «Pipeline stall» (en anglès). [Consulta: 13 novembre 2023].

- ↑ Hawthorne, Mel. «What Is a Pipeline Flush?» (en anglès americà), 08-10-2022. [Consulta: 13 novembre 2023].

- ↑ «Types of Pipeline Delay and Stalling» (en anglès). [Consulta: 13 novembre 2023].